均一なナノサイズ(ナノは10億分の1)の薄い膜を用いた酸化物半導体トランジスタの作製に、東京大学生産技術研究所の小林正治准教授(集積ナノエレクトロニクス)らのグループが成功した。素子を3次元的に積み上げる高集積化が可能となり、性能と信頼性も高いことから、ビッグデータを活用する社会サービスの展開などが期待できるという。

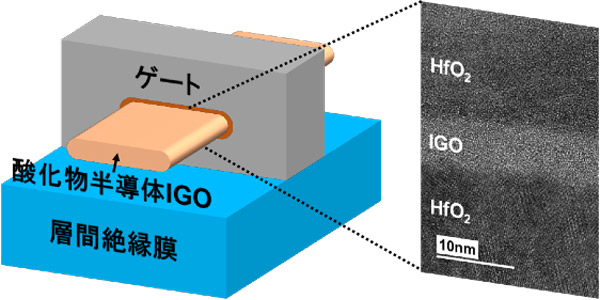

トランジスタで電荷を持つキャリア(電子や正孔)の通り道であるチャネル材料にナノ薄膜を採用した。原子層堆積法という手法で酸化インジウムと酸化ガリウムを交互に積層し、厚さ数ナノメートルの薄膜(IGO)を形成。この上下を酸化ハフニウム(HfO2)で挟み、ゲート電極で覆った。

こうして作った新型トランジスタは、現在主流のプレーナー(平面)型トランジスタに比べて駆動電流が2.6倍に増加し、キャリアの移動度が1.2倍に高まった。性能の劣化度を示す「バイアスストレス閾値電圧シフト」も低減し、高性能と高信頼性が両立しているという。

数多くのトランジスタを集積したプロセッサーとメモリーが従来のパソコンのように離れた場所にあると、データ処理に遅延時間などが生じる。AIやIoTといった昨今の先端技術ではプロセッサーとメモリーを同じ場所に置く必要がある。その究極的な形が、プロセッサーの直上に連続してメモリーを形成することだ。

小林准教授は「半導体の直上に、性能と信頼性の高いトランジスタは作れない、というこれまでの常識を克服できる技術といえる。大量のデータを扱う未来で、プロセッサーとメモリー間のやりとりが速い半導体技術は不可欠。実用化に向けて更なる改良を進めたい」と話した。

関連リンク

- 東京大学生産技術研究所プレスリリース「【記者発表】原子層堆積法を用いたナノシート酸化物半導体トランジスタを開発――半導体の高集積化・高機能化へ期待――」