今、ビッグデータや人工知能の研究に注目が集まり、情報通信技術を支える半導体デバイスの性能向上がますます求められている。これまでの半導体デバイスの性能向上は微細化により進められてきたが、それには限界があり、さらなる性能向上は難しい。そんな中、東北大学国際集積エレクトロニクス研究開発センター(CIES)の遠藤哲郎(えんどう てつお)センター長が率いるコンソーシアムでは、平面構造の半導体デバイスとは異なる縦型構造の複数のメモリセルを垂直方向に積層した三次元積層型メモリ(3D NANDメモリ)を発明、実用化に大きく寄与し、さらに、磁気制御によりデータを保存する高速大容量の次世代不揮発性メモリ(STT-MRAM)の製造装置と評価装置を製品化した。いずれも世界に先駆けて成し遂げられた功績であるため、この程、第14回産学官連携功労者表彰で「内閣総理大臣賞」を受賞した。次世代の情報通信機器を支える3D NANDメモリ、STT-MRAMとはいかなるデバイスで、今後、半導体産業にどのようなインパクトを与えようとしているのか。

―第14回産学官連携功労者表彰での「内閣総理大臣賞」の受賞、おめでとうございます。

ありがとうございます。

―受賞の知らせを受けて、最初にどのようにお感じになられましたか?

驚いた…というのが率直な感想でした。ただ一つ申し上げたいのは、今回の内閣総理大臣賞は、共同研究者の東京エレクトロン、キーサイト・テクノロジー・インターナショナルの方々と私の三人が受賞者ですが、集積エレクトロニクスの研究開発は、少人数でできるような分野ではありません。現在、東北大学国際集積エレクトロニクス研究開発センター(CIES)を拠点として形成されたコンソーシアムには、協力企業を含めて50社もの企業に参画いただいていますし、東北大学からは、私が率いる遠藤研以外にも多くの研究者が関わっています。そうした多くのメンバーのたゆまぬ努力が、内閣総理大臣賞の受賞という形で認められたことは、本当にうれしいです。

―では、具体的に、受賞された研究成果について伺いたいのですが、その前に、産学官連携功労者表彰とは、どのような賞でしょうか?

賞の名称が示す通り、産業界、学界、官界が連携して取り組んだ功績に対して与えられるものですが、研究としてどんなに優れた成果でも、論文を書いただけでは受賞の対象になることはなく、実用化された科学技術が対象になっています。その点で、今回は三つのポイントでご評価いただき、内閣総理大臣賞の受賞につながったと伺っています。まず、一つ目は三次元積層(3D NAND)技術を発明し、産学共同研究を通じてサンプル出荷など3D NANDメモリの工業製品化に貢献したこと。二つ目は高速大容量次世代不揮発性メモリ(STT-MRAM)の製造装置と評価装置の出荷に大きく貢献したこと。そして、三つ目は3D NANDやSTT-MRAMの研究開発を推進する国際的なオープンコンソーシアム型の研究体制の構築に対する評価です。

―一つ目の3D NANDとは、いかなる技術でしょうか?

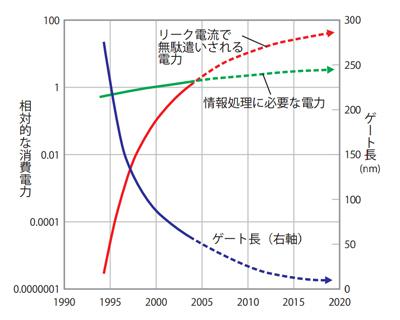

これまでの平面構造の半導体デバイスは、微細化することでその性能を向上させてきました。しかし、微細化には限界があり、平面構造の半導体デバイスに代わる新しい技術が求められていました。また、平面構造の半導体デバイスには、他にも大きな課題がありました。微細加工の限界に加えて、リーク電流の問題です。

集積回路に広く利用されている電界制御型コンデンサでは、シリコン半導体表面に積層されたゲート電極に電圧をかけると半導体界面に電気の通り道(チャネル)が生成し、駆動電気を流すことができます。この仕組みを利用して、ゲート電極に電圧をかけるかどうかで、シリコン半導体に電気を流すか流さないかを制御し、「1」か「0」かを示していました。しかし、半導体デバイスの微細化を進めた結果、ゲート電極を短くせざるを得ず、そのためにシリコン半導体の奥深くにまで電界制御を働かせることができず、意図しない電流の漏れが生じていたのです。

―リーク電流は無駄な電力消費ということになりますね?

だからこそ平面構造で発展してきた半導体デバイスの常識に囚われない縦型トランジスタの開発を進めてきました。円柱状のシリコン(シリコンピラー)に絶縁体の酸化層を形成した後、取り囲むようにゲート電極を形成し、拡散層もシリコンピラーの上下部に積層します。360度からゲート制御が働くためリーク電流が抑えられ、かつ、円柱全体が駆動電流を流すチャネルになるので低電圧で動作し、省エネルギーが実現します。

こうした縦型トランジスタの可能性は、他の研究機関でも検討されてはいましたが、実現の難しさから、本格的に研究開発に着手したところはほとんどありませんでした。私は前職の東芝でフラッシュメモリの開発に携わっていた頃から、情報端末を普及する上ではリーク電流の克服が欠かせないと考えていました。1995年に東北大学に着任してから縦型トランジスタの研究開発に着手し、2008年にJSTのCRESTに採択されて3D NANDメモリの開発を大きく前進させることができました。そして、13年には韓国のサムスンから、15年にはアメリカのインテル、マイクロン、日本の東芝から、3D NANDメモリのサンプル出荷が始まりました。

―量産化が始まった3D NANDメモリですが、その実装によって、私たちが使う情報端末はどのように変わっていくのでしょうか?

平面構造だった半導体デバイスと違って、縦型にするとメモリセルを積み重ねることができます。先程お話した通り、従来型平面構造の半導体デバイスは、微細化することで性能を高めてきたのですが、縦型になると積層化できるので、微細化だけに頼らずに飛躍的に集積化を向上させ、大容量化を実現することができます。例えば、今のUSBメモリは最大容量が512ギガバイトですが、私たちが開発した3D NANDメモリが利用されるようになると、10テラバイト程度の容量が実現します。すでに3D NANDメモリの量産体制が整い、出荷が始まっていますから、来年あたりには大容量のUSBメモリが現在と同程度の値段で売り出されることが期待されます。これだけ保存容量が大きくなると、超大容量と言われ、開発が進められているホログラムメモリ※1と比較しても、3D NANDメモリが最も安く、かつ大容量のストレージメモリ(データを長期保存する記憶装置)になります。先般、アメリカのグーグルがHDD(hard disc drive 磁気ディスクを高速回転させデータを記憶する装置)をやめて、SSD(solid state drive 駆動を要さず高速静音で半導体素子メモリに記憶する装置)に切り替えていくと発表※2しましたが、同様の動きは他社にも波及していくことでしょう。

※1 光の散乱を用いて対象物のスキャンや再現を行うホログラム技術を応用したデータ記憶装置。

※2 E. Brewer, L. Ying (Google, Inc.), “Disk for Data Centers -White paper for FAST 2016”, February 23, 2016

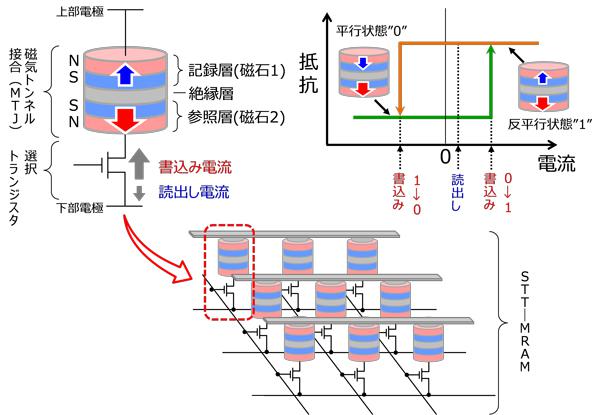

―では、二つ目に評価されたSTT-MRAMは、どういった成果だったのでしょうか?

STT-MRAMは、3D NANDのようなストレージメモリではなく、パソコンのメインメモリに使われるDRAM(Dynamic RAM)やキャッシュメモリに使われるSRAM(Static RAM)と同じように、コンピュータの心臓部で、数値演算などの高速情報処理で使うデータを記憶しておくための半導体メモリです。DRAMやSRAMは電荷を加えてデータを残す揮発性のメモリであるのに対して、STT-MRAMは磁気によって記録する不揮発性メモリです。そのため、電気の供給を止めるとデータが消えてしまうDRAMやSRAMとは異なり、電気を止めてもデータが保持されます。この不揮発性を活用して、STT-RAMは、従来のシリコン半導体の100分の1まで省電力化できると考えられています。

―なぜ、そこまでの省電力が可能なのでしょうか?

逆に質問させていただきますが、パソコンで文章を書くときに、1秒間に何回、キーボードをパンチできますか?

―ふだん意識したことはありませんが、どんなに頑張っても数回が精一杯だと思います。

では、計算しやすいように1秒間に10回パンチできると仮定しますね。つまり、100ミリ秒に1回のスピードでパンチすることになります。現在、一般的なパソコンの中央処理装置(Central Processing Unit: CPU)は3ギガヘルツ程度の動作スピードで動いていますから、100ミリ秒ごとに行われるキーパンチに伴う演算は、わずか1ナノ秒で終わってしまいます。演算そのものは、それだけ短時間で終わるのですが、DRAM、SRAMは電気の供給を止めるとデータが失われる揮発性メモリですから、1ナノ秒間の演算を終えても、100ミリ秒後のキーパンチまでの間もずっと電気を流しつづけなければなりません。一方、STT-MRAMは、先程お話した通り、磁気メモリで不揮発性なので、電気を供給しつづけなくてもデータが失われることはありません。そのためSTT-MRAMを導入したパソコンの場合、100ミリ秒ごとのキーパンチの度に、ほんの一瞬、1ナノ秒間だけ演算する間だけ電力を供給すればよく、後は電気の供給を止めることが可能です。

皆さんがお使いのパソコンは、ある一定時間何も操作しないと、勝手にスリープモードに入りますよね。それは、使わない間の無駄な電力消費を防ぐためなのです。しかし、DRAMやSRAMは揮発性で、電源を落とすと作業していたデータが失われてしまうので、その都度、ハードディスクに保存しているため、スリープモードから再起動すると、ハードディスクに保存したデータを呼び覚ますのに大きな演算が必要で、大きな電力を消費します。つまり、短時間でスリープモードに入ってしまうと、この大きな電力がスリープして節約する電力を超えてしまうのです。

これに対して、パソコンのメインメモリなどにSTT-MRAMが使われるようになると、作業している間のデータは不揮発性メモリで保存されていますから、キーパンチが行われている以外の時間はスリープに入り、キーパンチとともに瞬時に立ち上げられるようになります。その結果、パソコンの消費電力は100分の1程度に抑えられます。 しかし、このパワーマネージメントはコンピュータの中で自立的に行われますので、ユーザーである人間には、もはやスリープモードに入ったり復帰したりすることは感じられなくなります。

―それだけ省電力が進めば、私たちの身の回りの情報端末も大きく変化しそうですね。

現在、皆さんがお使いのスマートフォンやタブレット端末のバッテリーは、十分に充電したつもりでもいっぱい使うと一日すら持ちません。携帯電話に比べてスマートフォンでは高い演算能力が求められ、また、演算以外に消費される電力も大きいので頻繁に充電しなければならないのです。そのため、私は今なお古い携帯電話を手放せないのですが、今後、STT-MRAMが本格的に普及すれば、スマートフォンの消費電力は大幅に低下して、一度、十分にバッテリーを充電すれば一週間程度はもつようになるのではないかと思います。

このSTT-MRAMのメリットには多くの研究機関、メーカーが注目していて激しい開発競争が繰り広げられてきましたが、その中でいち早く私たちのコンソーシアムのメンバーである東京エレクトロンがSTT-MRAMの製造装置を、キーサイト・テクノロジー・インターナショナルが評価装置を製品化しました。デバイスメーカーがどんなにSTT-MRAMを製造したいと思っても、製造装置と、作られた半導体デバイスを検査する評価装置がなければ、工業製品として生産には入れません。世界に先駆けてSTT-MRAMの製造装置と評価装置を製品化できたことは大いに誇れる成果であり、今回の産学官連携功労者表彰の審査でも高く評価されたと伺っています。

―世界中の多くの研究機関、メーカーが研究開発に取り組んでいる中、なぜ遠藤先生らのコンソーシアムが、いち早く製造装置と評価装置の製品化を実現できたのでしょうか?

STT-MRAMの基盤技術となるスピントロニクスの世界を牽引する第一人者の研究者である大野英男(おおの ひでお)東北大学電気通信研究所所長・教授が、コンソーシアムに参加してくださったことが大きな力になりました。大野教授は磁気トンネル接合素子の研究※3でノーベル賞の候補になるほどのお方です。このように卓越したトップサイエンティストからトップエンジニアに至るまでの優れた頭脳を結集できたからこそ、STT-MRAMの製造装置と評価装置の製品化に漕ぎつけることができたのです。冒頭でお話した通り、集積エレクトロニクスの研究は少人数でできるものではありません。今回の受賞は、コンソーシアムのメンバー全員でいただいたものだと思っています。

※3 「論理集積回路用の高性能垂直磁化TMR素子の開発に成功」

(サイエンスライター 斉藤勝司)

(続く)

遠藤哲郎(えんどう てつお)氏のプロフィール

1962年生まれ。87年東京大学理学部卒。87年、東芝入社、NANDメモリの開発、事業化に従事。95年東北大学電気通信研究所講師、2007年同准教授、08年同教授、同年東北大学学際科学国際高等研究センター教授を経て、12年東北大学大学院工学研究科教授、現在に至る。10年東北大学省エネルギー・スピントロニクス集積化センター 副センター長兼務、12年東北大学国際集積エレクトロニクス研究開発センターセンター長兼務。縦型構造デバイス、SRAM・DRAM・3D NAND・STT-MRAMなどの高集積メモリ、モバイル・AI・IoTシステムに要求されるスピントロニクスベース超低消費電力化技術、GaN on Siベースパワーエレクトロニクス技術に関する研究に従事。日経BP LSI IP Design Award(研究助成部門)、11年度日本表面科学会論文賞、第31回JJAP論文賞、第6回応用物理学会フェロー、12 SSDM Paper Award、第14回内閣府産学官連携功労者表彰「内閣総理大臣賞」受賞。JST ACCEL「縦型BC-MOSFET による三次元集積工学と応用展開」研究代表者、及びJSPS研究拠点形成事業「半導体集積デバイス向け二次元電子・スピン材料研究拠点」コーディネーター